# Demo: Experimentation with Wideband Real-Time Adaptive Full-Duplex Radios

Alon S. Levin, Igor Kadota, Sasank Garikapati, Bo Zhang, Aditya Jolly, Manav Kohli, Mingoo Seok, Harish Krishnaswamy, and Gil Zussman Department of Electrical Engineering, Columbia University {alon.s.levin, ik2496, sg3734, bz2358, aj3036, mpk2138, ms4415, hk2532, gz2136}@columbia.edu

# ABSTRACT

We present a set of experiments utilizing *wideband real-time adaptive* full-duplex (FD) radios, demonstrating simultaneous transmission and reception on the same frequency channel. Each FD radio consists of a circulator-based antenna interface, a switchedcapacitor delay-line-based configurable Radio-Frequency Integrated Circuit (RFIC) that implements Self-Interference Cancellation (SIC), an FPGA that optimizes the RFIC configuration in under 1.1 sec and can adapt to environmental changes in under 0.3 sec, and a Software-Defined Radio (SDR) transmitting OFDM-like packets. We demonstrate a real-time adaptive FD radio that achieves the SIC necessary to reach the noise floor across a wide bandwidth of 50 MHz. Then, we use two FD radios to create a wireless link and showcase the superior FD throughput.

## **CCS CONCEPTS**

• Hardware → Wireless devices; *Radio frequency and wireless circuits*; • Networks → Network architectures; Network experimentation; Wireless access networks.

## **KEYWORDS**

Full-Duplex Wireless, Real-Time Adaptation, Self-Interference Cancellation, Software Defined Radio

#### **ACM Reference Format:**

Alon S. Levin, Igor Kadota, Sasank Garikapati, Bo Zhang, Aditya Jolly, Manav Kohli, Mingoo Seok, Harish Krishnaswamy, and Gil Zussman. 2023. Demo: Experimentation with Wideband Real-Time Adaptive Full-Duplex Radios. In ACM SIGCOMM 2023 Conference (ACM SIGCOMM '23), September 10, 2023, New York, NY, USA. ACM, New York, NY, USA, 3 pages. https: //doi.org/10.1145/3603269.3610853

# **1 INTRODUCTION**

Full-duplex (FD) wireless has drawn significant attention in recent years [3, 16, 17, 22] as an enabler of next-generation wireless networks, due to its potential to double the data rate at the Physical layer (PHY) and to provide additional cross-layer benefits throughout the networking stack. The main challenge associated with FD wireless is the strong self-interference (SI) signal at the receiver that

ACM SIGCOMM '23, September 10, 2023, New York, NY, USA

© 2023 Copyright held by the owner/author(s).

ACM ISBN 979-8-4007-0236-5/23/09.

https://doi.org/10.1145/3603269.3610853

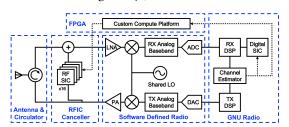

(a) Block diagram of the presented FD radio.

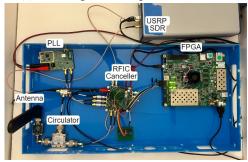

(b) Implementation of the presented FD radio.

Figure 1: The wideband real-time adaptive FD radio consisting of an antenna, a circulator, an RFIC canceller, an SDR, a PC running GNU Radio, and an FPGA. A phase-locked loop (PLL) synthesizer provides the clocks used by the RFIC.

needs to be suppressed to the noise floor, requiring 70 – 110 dB of SI cancellation (SIC) across the antenna, analog, and digital domains.

Achieving sufficient SIC is a challenge even at relatively narrow bandwidths (i.e.,  $\leq 20$  MHz) [1, 2, 7–9, 12]. To enable wideband FD, recent works [5, 11, 18, 23] have relied on the flexibility of programmable Radio-Frequency Integrated Circuits (RFICs). For example, in our prior work [18], we developed a switched-capacitor delay-line-based programmable IC that has sixteen RF taps, each with independently configurable gain and delay. The large RFIC configuration space, with over 10<sup>19</sup> possible parameter combinations, offers flexibility at the cost of complexity. An optimal RFIC configuration, computed using a PC (which could take over ten seconds), achieved 23 dB of isolation from the antenna interface and 30 dB of SIC from the RF taps over a 40 MHz bandwidth, as measured using a Vector Network Analyzer [18]. The RFIC presented in [18] was evaluated using test equipment and it was not integrated into a complete FD radio which would include digital SIC and a Software-Defined Radio (SDR) to transmit and receive actual data. Accordingly, two important challenges that are under-explored in related works, including [18], are: (i) to design a real-time adaptive controller that enables a highly-complex programmable RFIC to

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

achieve and sustain sufficient SIC even when the SI is time-varying; and (ii) to integrate the RFIC (along with its real-time controller) into a complete FD radio that can transmit data over an actual link.

We previously presented two narrowband FD radios within the scope of the Columbia FlexICoN project [24], achieving FD communication across 5 MHz with a single-tap amplitude- and phase-based RF SI canceller [15] and 20 MHz with a two-tap frequency-domain equalization-based RF SI canceller [6]. In this demonstration, we present a wideband FD radio that adaptively controls the RFIC from [18] in real time, achieving 70 dB SIC across a wide bandwidth of 50 MHz through a combination of circulator isolation, analog RFIC cancellation, and digital SIC, reaching the noise floor of the FD radio at -80 dBm. The complete RFIC optimization process is performed in under 1.1 sec, and each fine-tuning adaptation step is performed in under 0.3 sec.

# 2 DESIGN AND IMPLEMENTATION

Figures 1(a) and 1(b) show the block diagram and implementation of the FD radio, consisting of a circulator-based antenna interface, an RFIC canceller, an FPGA, and a USRP SDR platform controlled from a PC running GNU Radio.

**RFIC Canceller.** SI at the FD receiver can be very strong, causing nonlinearities at the Low Noise Amplifier (LNA) and clipping at the Analog to Digital Converter (ADC). It is therefore crucial to achieve sufficient SIC directly after the antenna interface. To enable wideband SIC, the RFIC canceller [18] leverages its sixteen RF taps with programmable gains and delays in order to recreate the large SI channel delay spreads with fine resolution. The programmable delays are implemented in a small form factor by means of switched-capacitor delay-lines, ranging from 0.25 ps to 9 ns in steps of 0.25 ps. The programmable gains are implemented using capacitor-stacking and range from 0 to 1 in 6-bit quantization steps.

**FPGA platform.** The FD radio utilizes a Zynq UltraScale+ MP-SoC ZCU104 Evaluation Board [25] to adaptively control the RFIC in real-time. Using a brute force algorithm to search for the optimal RFIC configuration within the  $> 10^{19}$  possible gain and delay combinations is impractical. To quickly and adaptively control the RFIC, we implement a closed-loop algorithm with two phases – coarse-tuning and fine-tuning – both of which rely on the offline characterization of the RF taps which are stored in the FPGA's memory. During coarse-tuning, the FPGA employs Orthogonal Matching Pursuit (OMP) [10] with Constrained Linear Least-Squares to select a subset of the RF taps and corresponding configuration that maximizes SIC. In each subsequent fine-tuning step, the FPGA uses Projected Gradient Descent to adjust the gains of the RFIC.

**SDR platform.** The FD radio employs a USRP-2974 for transmission and reception of OFDM-like data packets [4] encapsulated with Zadoff-Chu pilot symbols for robust synchronization [13]. The SDR and FPGA are both controlled from an Ubuntu 20.04 computer running GNU Radio 3.8 and UHD 4.2 [20, 21]. The custom-made GNU Radio flowgraph estimates the SI channel across the bandwidth of interest [14, 19], and sends it to the FPGA via USB. The FPGA uses the SI channel estimate to search for the optimal RFIC configuration, and then sends the selected configuration to the RFIC canceller via serial communication. Moreover, the flowgraph uses the SI channel estimate to perform digital SIC [6].

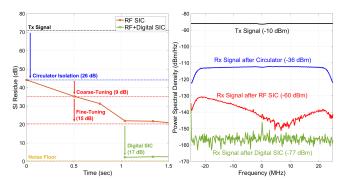

Figure 2: Evolution of the RF and combined RF & digital cancellation over time. The circulator provides 26 dB of isolation. Initial coarse-tuning (0.5 sec) improves SIC by 9 dB. Two fine-tuning steps (2 × 0.3 sec) add 15 dB, and the total SIC (RF + digital) converges to the noise floor.

# **3 DEMONSTRATIONS**

Experiment 1: Wideband Adaptive FD Radio. This demonstration showcases the capability of the FD radio to quickly achieve and sustain wideband SIC even when the SI is time-varying. In this experiment, the SDR operates at a center frequency of 850 MHz and with a bandwidth of 50 MHz, which lies within the operating frequency of the circulator, and transmits at -10 dBm, which is close to the maximum power admissible by the RFIC [18]. Participants can observe the transmitted and received signals in the time and frequency domains, before and after SIC is applied. In addition, participants visualize the SIC evolution over time, as shown in Figure 2, together with the evolution of the RFIC and digital SIC parameters selected by the optimization algorithms. Furthermore, participants are allowed to modify the environmental conditions near the antenna, requiring the FD radio to adapt quickly. From Figure 2 it can be seen that coarse-tuning takes less than 0.5 sec and fine-tuning less than 0.3 sec. Notice that each of those periods includes packet transmission and reception, SI channel estimation, FPGA computation, and RFIC configuration.

**Experiment 2: Throughput Gain of FD Link.** In this demonstration, we use two FD radios to establish a wireless link in which both SDRs transmit and receive OFDM-like packets. The center frequency, bandwidth, and power of both SDRs are the same as for Experiment 1. Participants will observe the correct reception of data packets on both FD radios, and measure the improved throughput of the FD link when compared to a Half-Duplex (HD) link. By comparing HD and FD operations, participants will observe that the bit error rate is not degraded due to wideband SIC.

#### ACKNOWLEDGEMENTS

This work was supported in part by the DARPA WARP program, NSF grants OAC-2029295, EEC-2133516, AST-2232455, and CNS-2148128, and by funds from federal agency and industry partners as specified in the NSF Resilient & Intelligent NextG Systems (RINGS) program. A.S.L. was supported by the DoD through the NDSEG Fellowship Program. M.K. was supported by the NSF GRFP (DGE-2036197). We thank Samuel Cohen, Ahuva Bechhofer, and Enzo Olivier Schulze for their contributions to this work.

Levin et al

Demo: Wideband Real-Time Adaptive Full-Duplex Radios

### REFERENCES

- [1] Hany Abolmagd, Raghav Subbaraman, Omid Esmaeeli, Yeswanth Guntupalli, Ahmad Sharkia, Dinesh Bharadia, and Sudip Shekhar. 2023. A Hierarchical Self-Interference Canceller for Full-Duplex LPWAN Applications Achieving 52–70-dB RF Cancellation. *IEEE Journal of Solid-State Circuits* 58, 5 (2023), 1323–1336.

- [2] Muhammad Sohaib Amjad and Falko Dressler. 2020. Software-Based Real-Time Full-Duplex Relaying: An Experimental Study. IEEE Transactions on Green Communications and Networking 4, 3 (2020), 647–656.

- [3] Dinesh Bharadia, Emily McMilin, and Sachin Katti. 2013. Full Duplex Radios. In Proc. ACM SIGCOMM'13.

- [4] Bastian Bloessl, Michele Segata, Christoph Sommer, and Falko Dressler. 2013. An IEEE 802.11a/g/p OFDM Receiver for GNU Radio. In Proc. SRIF'13.

- [5] Yuhe Cao, Xuanzhen Cao, Hyungjoo Seo, and Jin Zhou. 2020. An Integrated Full-Duplex/FDD Duplexer and Receiver Achieving 100MHz Bandwidth 58dB/48dB Self-Interference Suppression Using Hybrid-Analog-Digital Autonomous Adaptation Loops. In Proc. IEEE/MTT-S IMS'20.

- [6] Tingjun Chen, Mahmood Baraani Dastjerdi, Jin Zhou, Harish Krishnaswamy, and Gil Zussman. 2019. Wideband Full-Duplex Wireless via Frequency-Domain Equalization: Design and Experimentation. In Proc. MobiCom'19.

- [7] Jung Il Choi, Mayank Jain, Kannan Srinivasan, Phil Levis, and Sachin Katti. 2010. Achieving Single Channel, Full Duplex Wireless Communication. In Proc. MobiCom'10.

- [8] Minkeun Chung, Min Soo Sim, Jaeweon Kim, Dong Ku Kim, and Chan-byoung Chae. 2015. Prototyping Real-Time Full Duplex Radios. *IEEE Communications Magazine* 53, 9 (2015), 56–63.

- [9] Melissa Duarte, Ashutosh Sabharwal, Vaneet Aggarwal, Rittwik Jana, K. K. Ramakrishnan, Christopher W. Rice, and N. K. Shankaranarayanan. 2014. Design and Characterization of a Full-Duplex Multiantenna System for WiFi Networks. *IEEE Transactions on Vehicular Technology* 63, 3 (2014), 1160–1177.

- [10] Michael Elad. 2010. Sparse and Redundant Representations: From Theory to Applications in Signal and Image Processing. Springer.

- [11] Ali Ershadi and Kamran Entesari. 2020. A 0.5-to-3.5-GHz Full-Duplex Mixer-First Receiver with Cartesian Synthesized Self-Interference Suppression Interface in 65-nm CMOS. *IEEE Transactions on Microwave Theory and Techniques* 68, 6 (2020), 1995–2010.

- [12] Evan Everett, Clayton Shepard, Lin Zhong, and Ashutosh Sabharwal. 2016. Soft-Null: Many-Antenna Full-Duplex Wireless via Digital Beamforming. *IEEE Trans*actions on Wireless Communications 15, 12 (2016), 8077–8092.

- [13] Malik Muhammad Usman Gul, Xiaoli Ma, and Sungeun Lee. 2015. Timing and Frequency Synchronization for OFDM Downlink Transmissions Using Zadoff-Chu Sequences. *IEEE Transactions on Wireless Communications* 14, 3 (2015), 1716–1729.

- [14] Edward Kassem, Roman Marsalek, and Jiri Blumenstein. 2018. Frequency Domain Zadoff-Chu Sounding Technique for USRPs. In Proc. IEEE ICT'18.

- [15] Manav Kohli, Tingjun Chen, Mahmood Baraani Dastjerdi, Jackson Welles, Ivan Seskar, Harish Krishnaswamy, and Gil Zussman. 2021. Open-Access Full-Duplex Wireless in the ORBIT and COSMOS Testbeds. *Computer Networks* 199 (2021), 108420.

- [16] Kenneth E Kolodziej, Bradley T Perry, and Jeffrey S Herd. 2019. In-Band Full-Duplex Technology: Techniques and Systems Survey. *IEEE Transactions on Microwave Theory and Techniques* 67, 7 (2019), 3025–3041.

- [17] Harish Krishnaswamy and Gil Zussman. 2016. 1 Chip 2x the Bandwidth. IEEE Spectrum 53, 7 (2016), 38-54.

- [18] Aravind Nagulu, Sasank Garikapati, Mostafa Essawy, Igor Kadota, Tingjun Chen, Arun Natarajan, Gil Zussman, and Harish Krishnaswamy. 2021. Full-Duplex Receiver with Wideband Multi-Domain FIR Cancellation Based on Stacked-Capacitor, N-Path Switched-Capacitor Delay Lines Achieving >54dB SIC Across 80MHz BW and >15dBm TX Power-Handling. In Proc. IEEE ISSCC'21.

- [19] John C. L. Ng, Khaled Ben Letaief, and Ross D. Murch. 1998. Complex Optimal Sequences with Constant Magnitude for Fast Channel Estimation Initialization. IEEE Transactions on Communications 46, 3 (1998), 305–308.

- [20] GNU Radio. 2019. GNU Radio. https://www.gnuradio.org/

- [21] Ettus Research. 2022. USRP Hardware Driver (UHD) software. https://github. com/EttusResearch/uhd

- [22] Ashutosh Sabharwal, Philip Schniter, Dongning Guo, Daniel W Bliss, Sampath Rangarajan, and Risto Wichman. 2014. In-Band Full-Duplex Wireless: Challenges and Opportunities. *IEEE Journal on Selected Areas in Communications* 32, 9 (2014), 1637–1652.

- [23] Vaibhav Singh, Susnata Mondal, Akshay Gadre, Milind Srivastava, Jeyanandh Paramesh, and Swarun Kumar. 2020. Millimeter-Wave Full Duplex Radios. In Proc. MobiCom'20.

- [24] Columbia University. 2023. The FlexICoN Project. https://flexicon.ee.columbia. edu/

- [25] Xilinx. 2018. Zynq Ultrascale+ MPSoC ZCU104 Evaluation Kit. https://www. xilinx.com/products/boards-and-kits/zcu104.html